Mémoire dynamique 1 bit

On appelle mémoire un composant électronique permettant de stocker une information sous forme binaire. On distingue les mémoires à lecture seule appelées ROM pour Read Only Memory et les mémoires à lecture/écriture appelées improprement RAM pour Random Access Memory. Le contenu des mémoires à lecture seule est fixé lors de la fabrication en usine et reste dans la mémoire lorsque celle-ci n'est pas alimentée. Au contraire, les mémoires à lecture/écriture sont volatiles. Le contenu est perdu dès qu'elles ne sont plus alimentées.

Il existe des mémoires intermédiaires entre les RAM et les ROM. Elles se comportent comme des ROM dans la mesure où elles ne perdent pas leur contenu sans alimentation mais ce contenu peut toutefois être modifié par un processus spécial. Le contenu d'une EPROM est effacé par une exposition aux ultra-violets. Un nouveau contenu peut alors être écrit par un appareil spécialisé. Les EEPROM peuvent être reprogrammées de manière électrique. Les mémoires flash sont des EEPROM dont la reprogrammation est rapide (d'où leur nom).

Les mémoires des tous premiers ordinateurs étaient magnétiques. Les mémoires sont maintenant des composants électroniques à base de transistors. Il existe deux types de mémoires qui se distinguent par leur technique de fabrication : les mémoires dynamiques et les mémoires statiques. Il s'agit dans les deux cas de mémoires volatiles qui nécessitent une alimentation pour conserver leur contenu. La mémoire dynamique est appelée DRAM pour Dymanic RAM par opposition à la mémoire statique appelée SRAM pour Static RAM.

| Mémoire dynamique | Mémoire statique |

|---|---|

| Grande densité d'intégration | Petite densité d'intégration |

| Bon marché | Chère |

| Lente | Rapide |

| Mécanisme de rafraîchissent |

Comme son coût est moindre et que sa densité d'intégration est supérieure, la mémoire dynamique est utilisée pour la mémoire principale de l'ordinateur. Par contre, la mémoire statique est utilisée pour les caches en raison de sa plus grande vitesse.

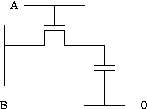

Chaque élément de mémoire dynamique est formé d'un condensateur et d'un transistor de commande (cf. figure ci-dessous). La ligne A est appelée ligne de commande ou ligne d'adresse. La ligne B est la ligne de donnée sur laquelle est lu ou écrit le bit d'information. Le bit d'information est représenté par la charge du condensateur. Lorsque la ligne de commande est à 0, le condensateur est isolé de la ligne de donnée et la charge reste prisonnière du condensateur. Au contraire, lorsque la ligne de commande est à 1, on peut lire le bit en détectant la charge ou écrire un nouveau bit en forçant la ligne de donnée à une valeur.

Mémoire dynamique 1 bit

Il existe deux types principaux de mémoire dynamique qui se distinguent par leur façon de communiquer avec le processeur. Les premières mémoires dynamiques étaient asynchrones alors que les mémoires actuelles sont synchrones. Ces dernières sont appelées SDRAM pour Synchronous Dymanic RAM.

Lorsque le processeur lit une donnée dans une mémoire asynchrone, celui-ci lui envoie l'adresse puis attend que celle-ci lui retourne la donnée à cette adresse. Plusieurs cycles horloge peuvent s'écouler avant que la donnée ne parvienne au processeur. Après réception de la donnée, le processeur peut à nouveau demander une autre donnée à la mémoire. À chaque requête à la mémoire, le processeur reste inactif en attendant que la donnée n'arrive.

Dans le cas de mémoire synchrone, le processeur peut envoyer à la mémoire une nouvelle requête de lecture ou d'écriture avant que celle-ci n'ait fini de traiter la première requête. Les demandes successives sont alors exécutées séquentiellement par la mémoire. Chaque requête est reçue pendant un cycle d'horloge et les données sont délivrées quelques cycles d'horloge plus tard. Le nombre de cycles d'horloge entre la requête et la donnée est fixe. De cette manière, le processeur peut déterminer à quelle requête correspond chaque donnée. Le principe de fonctionnement d'une mémoire synchrone est identique au pipeline utilisé pour réaliser un processeur. La mémoire est organisée comme une chaîne où sont traitées les requêtes. La mémoire traite simultanément plusieurs requêtes qui se trouvent à des étapes différentes de la chaîne. Le traitement d'une seule requête prend plusieurs cycles d'horloge mais une requête est traitée à chaque cycle.

Parmi les mémoires synchrones, on distingue encore plusieurs variantes. Les mémoires SDR SDRAM pour Single Data Rate SDRAM reçoivent une requête à chaque cycle d'horloge. Les mémoires DDR SDRAM pour Double Data Rate DRAM permettent de doubler le débit de données entre le processeur et la mémoire. Une requête est encore traitée à chaque cycle d'horloge mais chaque requête concerne deux mots consécutifs en mémoire. Le premier mot est transmis sur le front montant du signal d'horloge alors que le second est transmis sur front descendant du signal d'horloge. Les mémoires DDR2 SDRAM doublent encore le débit de données en traitant quatre mots consécutifs en mémoire à chaque requête.

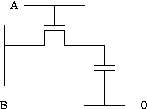

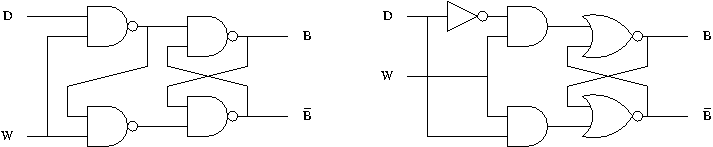

Chaque élément de mémoire statique est formé de six transistors. Quatre de ces six transistors constituent deux inverseurs mis tête-bêche et les deux derniers, commandés par la ligne d'adresse A, relient les inverseurs aux lignes de données

Mémoire statique 1 bit

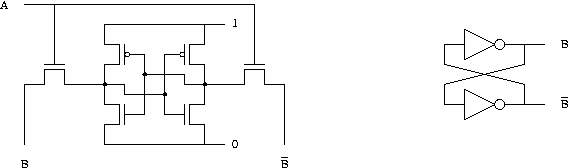

Le verrou SR est un bit de mémoire muni de deux entrées S et R permettant de le positionner à 1 (Set) ou à 0 (Reset). Ce circuit peut être réalisé avec deux portes nor ou deux portes nand. Dans ce dernier cas, les commandes S et R sont inversées : elles sont actives pour la valeur 0 et inactive pour la valeur 1.

Verrou SR

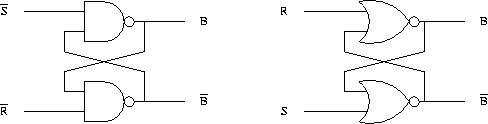

L'inconvénient principal du verrou SR est que son état n'est pas spécifié si les deux commandes S et R sont activées simultanément. Le verrou D résout ce problème. Ce verrou a deux entrées D (pour Data) et W (pour Write). La première entrée donne la valeur qui doit être écrite dans le bit de mémoire et la seconde entrée valide l'entrée D. Si W vaut 0, rien n'est écrit dans la mémoire et son état reste inchangé. Si au contraire W vaut 1, la valeur de D est écrite dans la mémoire.

Verrou D (mémoire 1 bit)

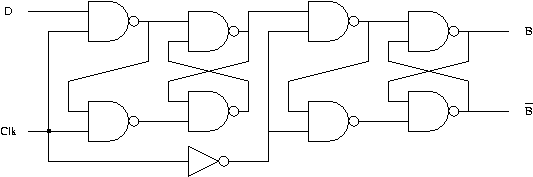

La bascule D est obtenue en mettant en série deux verrous D avec des entrées W en opposition (négation l'une de l'autre). L'entrée W du premier verrou D est l'entrée Clk de la bascule et sa sortie est l'entrée D du second verrou D. L'entrée W du second verrou est la négation ¬Clk de l'entrée Clk de la bascule. Quand l'entrée Clk de la bascule vaut 1, son entrée D est écrite dans le premier verrou pendant que le second verrou reste inchangé. Quand l'entrée Clk de la bascule vaut 0, le premier verrou reste inchangé et son état est écrit dans le second verrou. Il s'agit d'une sorte de bufferisation qui permet de lire et d'écrire simultanément dans une mémoire 1 bit. Pendant que Clk vaut 1, le premier verrou reçoit la nouvelle valeur pendant que l'ancienne valeur est lue dans le second verrou. Pendant que Clk vaut 0, la nouvelle valeur est transférée dans le second verrou.

Les bascules D sont utilisées dans les circuits séquentiels et elle reçoivent alors le signal d'horloge sur l'entrée Clk (pour Clock).

Bascule D (mémoire 1 bit avec bufferisation)

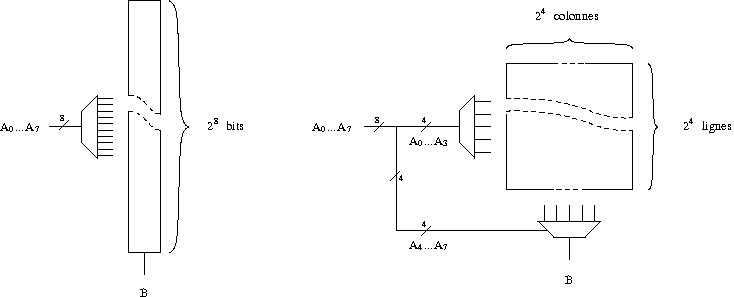

La mémoire peut être vue comme organisée en grille. Chaque ligne correspond à une adresse. Le nombre de lignes est donc une puissance de deux. Ce nombre est égal à 2k où k est le nombre de lignes d'adresse. Chaque colonne de la grille correspond à un des bits de la donnée transmise. Le nombre de colonnes peut être quelconque même si dans la pratique, c'est aussi une puissance de deux, souvent 8, 16 ou 32.

Dans le cas d'une mémoire 1 bit, il y a un intérêt à ne pas l'organiser comme une seule colonne selon le principe précédent mais encore sous forme d'une grille. Il y a alors un gain sur le nombre de portes logiques utilisées pour le décodage des adresses.

Organisations colonne et grille

d'une mémoire 28 × 1 bits

Soit par exemple une mémoire 28 × 1 bits. Si elle est organisée selon une seule colonne, on a un décodeur à 8 entrées qui utilise donc 256 = 28 portes et logique ayant chacune 8 entrées. Cette même mémoire peut être organisée selon une grille 16 × 16. Les quatre premiers bits A0…A3 sont envoyés sur un décodeur pour sélectionner la ligne parmi les 16 = 24 lignes. Un multiplexeur commandé par les quatre derniers bits A4…A7 permet de sélectionner le bit parmi les 16 bits provenant des 16 colonnes. Le décodeur et le multiplexeur utilisent chacun 16 portes et logique ayant chacune 3 ou 4 entrées. Ceci fait un total de 32 portes dans l'organisation en grille et donc un gain de 224 portes portes par rapport à l'organisation en colonne. Dans le cas de mémoires ayant un nombre très important de bits, le gain est bien supérieur.

Dans le cas d'une grille, celle-ci n'a pas besoin d'être carrée comme dans l'exemple. Il est possible d'utiliser tous les intermédiaires entre une seule colonne et un carré. Par contre, ce sont les grilles carrées qui procurent le plus grand gain en nombre de portes logiques. Dans l'organisation colonne, le nombre de portes utilisées est proportionnel au nombre de bits de la mémoire. Chaque bit mémoire nécessite un seul transistor alors que chaque porte logique nécessite plusieurs transistors. Du coup, l'essentiel des transistors est finalement utilisé pour le décodage des adresses. Dans l'organisation en grille, le nombre de portes logiques utilisées pour le décodage est proportionnel à la racine carrée √n de n où n est le nombre de bits de la mémoire.

La plupart des mémoires utilisées dans les ordinateurs sont des mémoires 1 bit. Pour obtenir une mémoire dont chaque mot est un octet, il est nécessaire d'assembler huit boîtiers. Ceux-ci sont mis en parallèle dans la mesure où ils reçoivent tous la même adresse. Par contre, chacun des boîtiers reçoit une seule ligne du bus de donnée.

Pour construire une mémoire ayant 2k' mots avec des boîtiers mémoire 2k mots, il faut utiliser 2k'-k boîtiers. Les k' bits d'adresses sont alors distribués de la manière suivante. Les k bits de poids faibles A0…Ak-1 sont envoyés sur tous les boîtiers. Les k'-k bits de poids fort Ak…Ak'-1 arrivent sur un décodeur permettant de sélectionner un seul des 2k'-k boîtiers mémoire. Tous les bits du bus de données sont reliés à chacun des boîtiers. Ceci est possible aussi bien en lecture qu'en écriture car les entrée/sorties des boîtiers sont dans un état dit haute impédance lorsque le circuit n'est pas sélectionné.

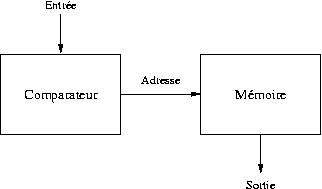

Les mémoires associatives permettent de stocker un ensemble de paires (clés,valeurs), de rechercher en temps constant si une valeur est associée à une clé. Un tel dispositif est utilisé dans les routeurs réseaux et surtout pour le Translation Lookaside Buffer de la mémoire virtuelle. La mémoire associative sert alors à traduire les adresses virtuelles en adresses physiques.

Principe de la mémoire associative